Cyclone V Soc

Cyclone® V FPGAs provide the industry’s lowest system cost, lowest power FPGA solution as well as small formfactor package options (as small as 11x11 mm2) These advantages, along with its performance and logic utilization, result in devices optimized for differentiating your highvolume applications.

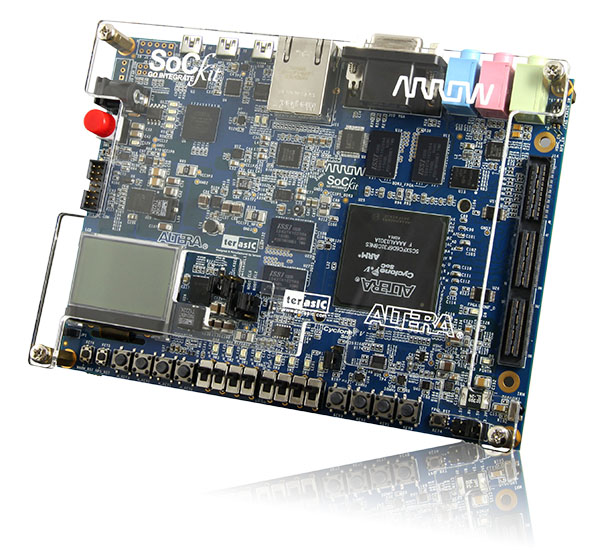

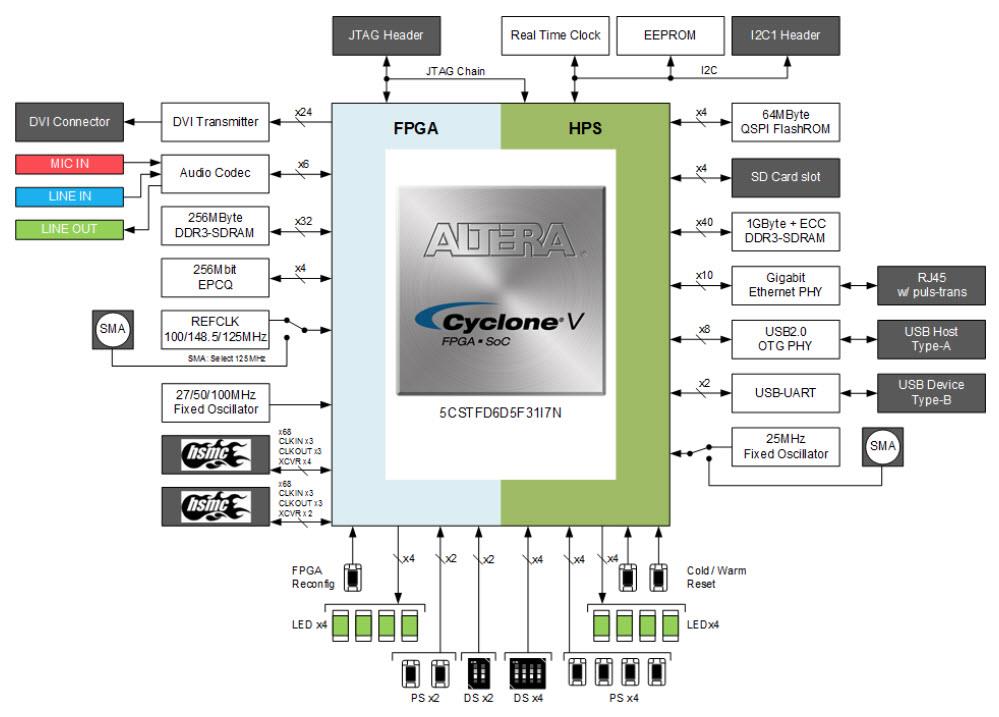

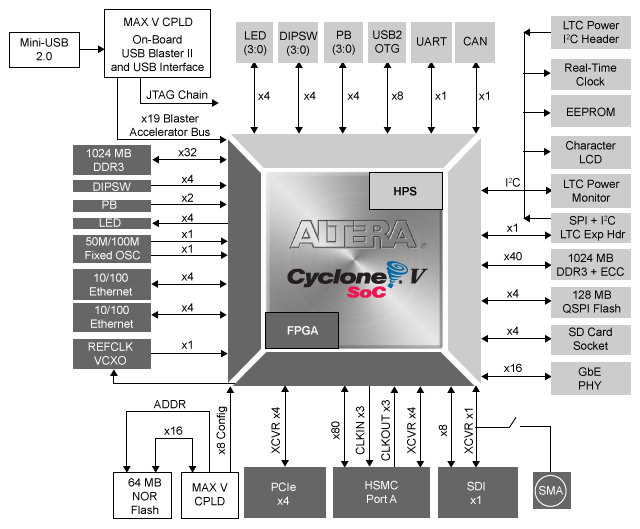

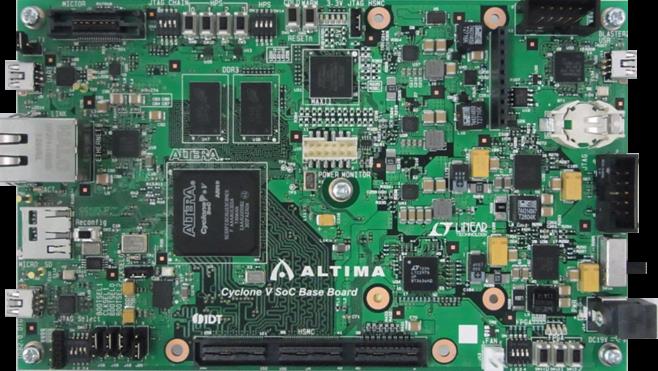

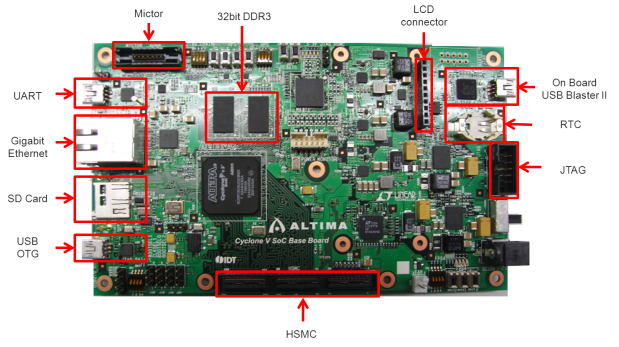

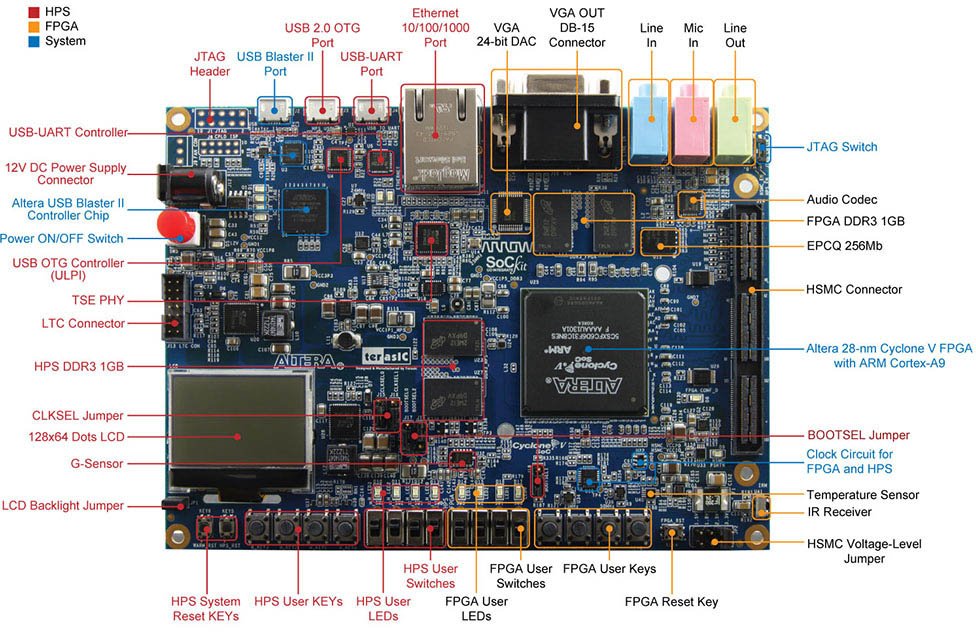

Cyclone v soc. Cyclone V SoC Altera Cyclone V SoC Board;. Chips, Ports, and Features connected to FPGA Integrated USBBlaster II JTAG cable;. Arrow SoCKit User Manual July 17 Edition;.

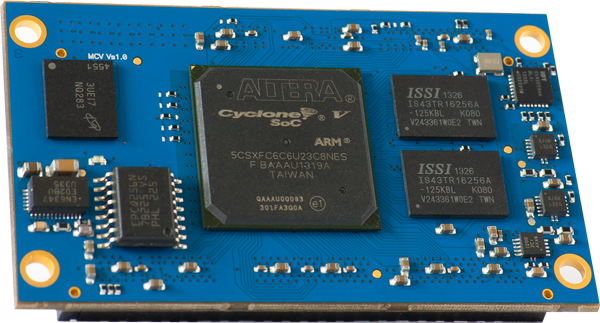

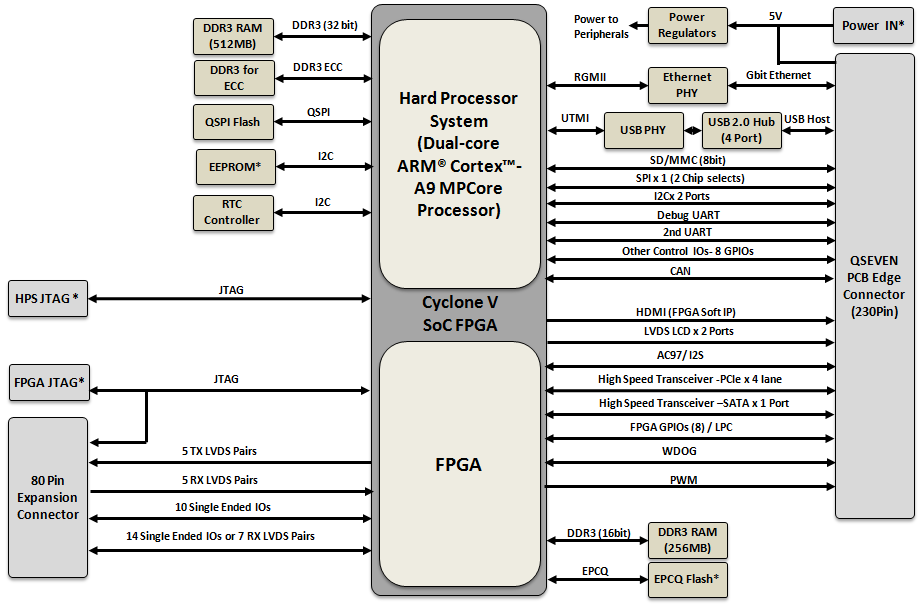

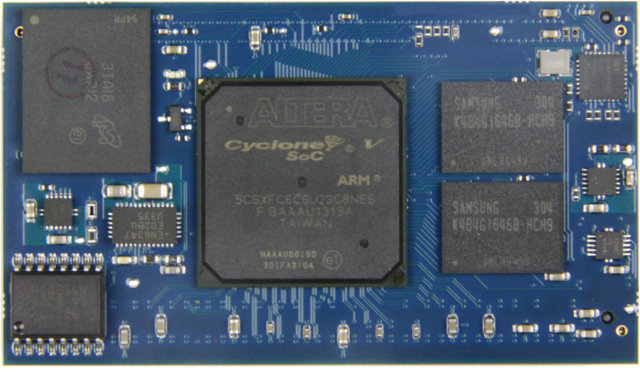

SoC – Intel PSG / Altera Cyclone V SE 5CSEBA6U19I7N with a dualcore ARM Cortex processor @ up to 800 MHz and FPGA fabric with 110K Logic Elements;. MCV offers the full flexibility of the Altera Cyclone V SoC FPGA family It integrates an ARMbased hard processor system (HPS) consisting of processor, peripherals, and memory interfaces with the FPGA fabric using a highbandwidth interconnect backbone The Altera SoCs combine the performance and power savings of hard intellectual property (IP) with the flexibility of. The MitySOM5CSx Development Kit supports Critical Link’s Altera Cyclone V SoC based modules Each kit includes a compatible MitySOM5CSx module (see Purchase table below for compatible modules) and a base board that features an array of interfaces and expansion headers such as USB, Debug RS232 to USB Console, Full HSMC Expansion Connector, Partial HSMC Expansion Connector, PCIe x4.

The Cyclone® V SoC FPGA includes a sophisticated highperformance multicore ARM* Cortex* processor This processor can be used for a wide range of functions from very simple baremetal applications running on one of the available cores to highbandwidth, lowlatency, realtime operations. The Cyclone ® V SoC Development Kit offers a quick and simple approach to develop custom ARM * processorbased SoC designs accompanied by Intel's lowpower, lowcost Cyclone V FPGA fabric This kit supports a wide range of functions, such as Processor and FPGA prototyping and power measurement. How to write a C/C application and run on the Altera Cyclone V SoC Dev Kit using ARM DS5 AE Follow Intel FPGA to see how we’re programmed for success and.

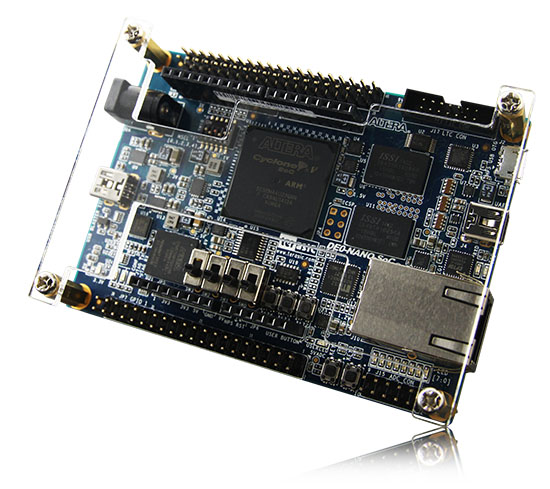

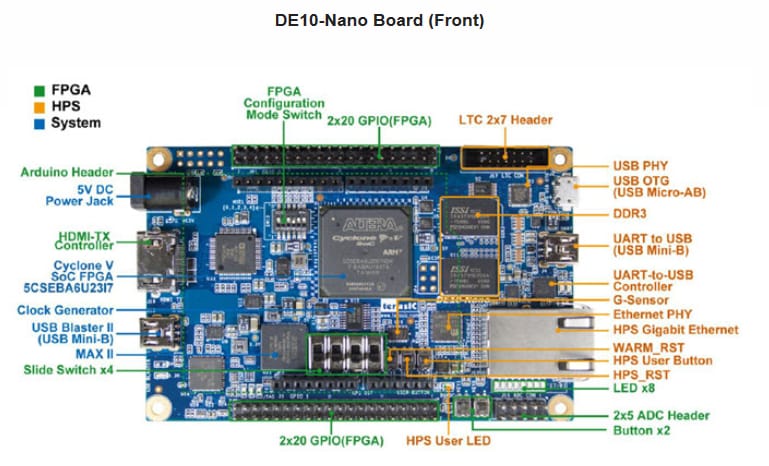

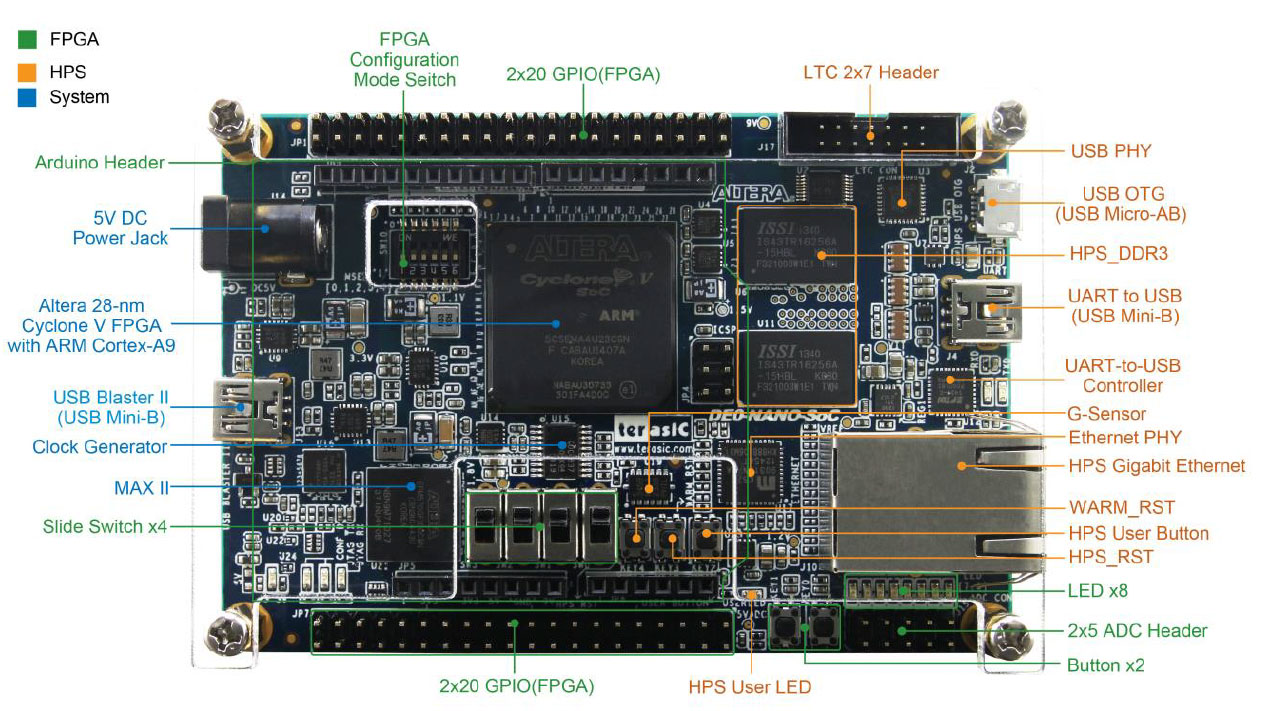

Configuration sources SD Card, JTAG;. Overview The DE10Nano development board features a Cyclone® V SoC FPGA combined with a wide range of peripheral devices and I/O expansion headers to create a powerful development platform This lowcost kit serves an interactive, webbased "guided tour" that lets you quickly learn the basics of SoC FPGA development and provides an excellent platform on which to develop your own SoC FPGA. Hi, I designed a circuit board using 5CSEBA5U23I7,encountered some problems 1In the Programmer,when I clicked on "Auto Detect", I cannot get the correct JTAG ID as shown in the picture 2When I use the JTAG chain debugger, the result is as shown in the attached picture 3The chip heats up seve.

CYCLONE V SoC BANK 6 (HPS) 5 5 4 4 3 3 2 2 1 1 D D C C B B A A VCCIO = 33V VCCIO = 33V VCCIO = 33V VCCIO = 33V 10 5 3 3 GPIO HDMI TX User Interface (FPGA) 5 5 1 3 3 6 3 3 SD Card Interface. System on Module with Altera Cyclone V SoC Borax SOM is a system on module card integrating Altera® Cyclone® V SoC and necessary memory, power and external interfaces on a very small size card Cyclone V SoC is a new SoC tightly coupling with Dualcore ARM Cortex and FPGA fabric, enabling easy development of complex systems with advanced application processing and flexible hardware using. Cyclone® V SE SoC FPGA product listing with links to detailed product features and specifications.

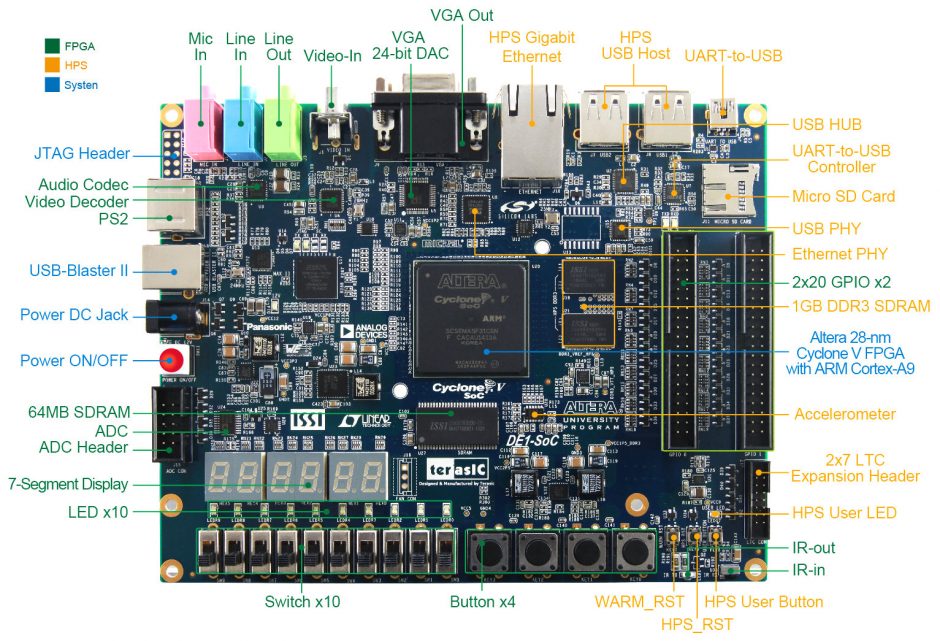

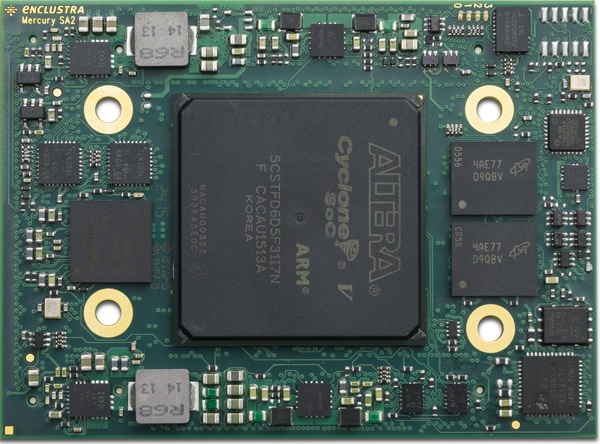

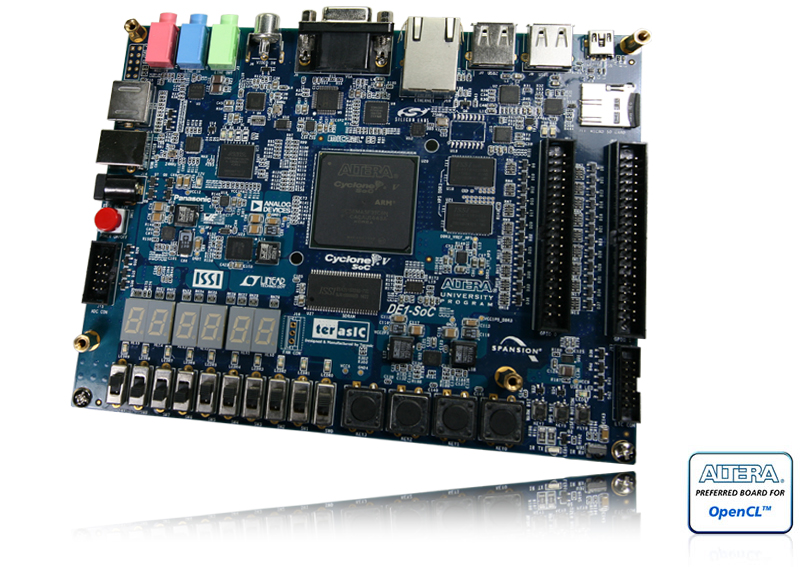

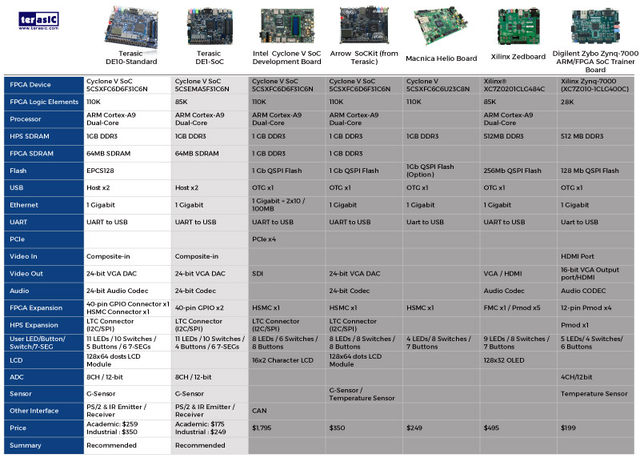

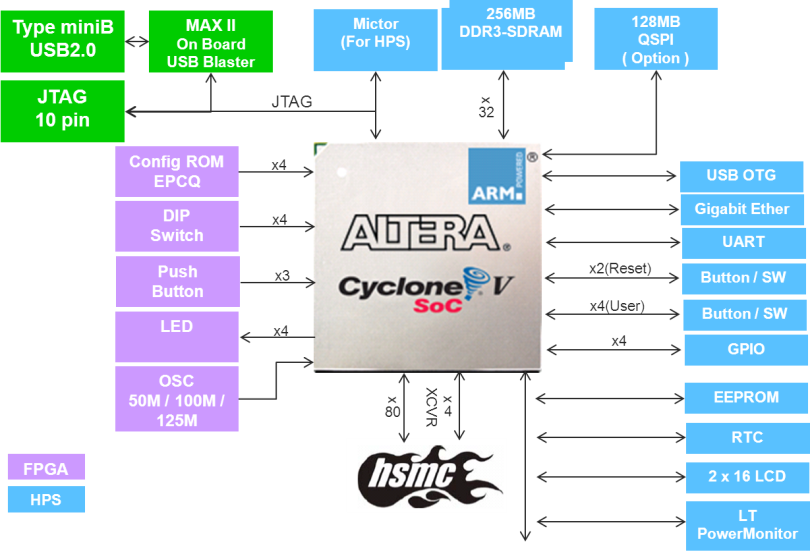

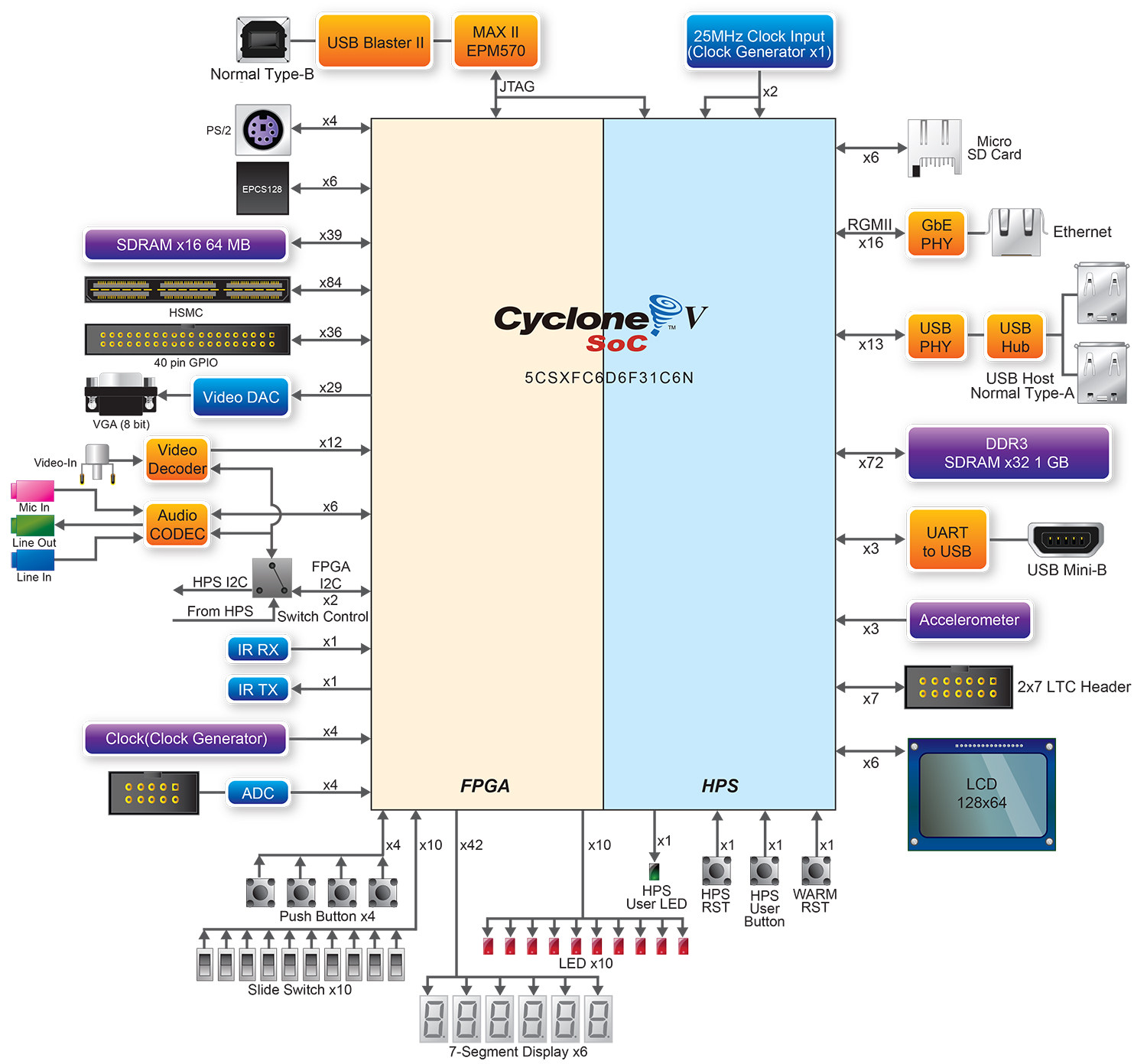

Dualcore ARM Cortex (HPS) 85K Programmable Logic Elements;. Cyclone V SoC with Dualcore ARM Cortex (HPS) FPGA SDRAM, VGA Out, VideoIn, ADC Header, GPIO Header HSMC Headers HPS DDR3, USB Host, MicroSD Socket, Ethernet, Accelerometer, UARTtoUSB, LTC Header Support Linux BSP and openCL BSP. The Mercury SA1 systemonchip (SoC) module combines Intel's Cyclone V ARM Processorbased SoC FPGA with fast DDR3 SDRAM, eMMC flash, quad SPI flash, a Gigabit Ethernet PHY and an RTC and thus forms a highperformance embedded processing solution, combining the flexibility of a CPU system with the raw, realtime parallel processing power of an.

Cyclone® V FPGA Family Cyclone® V FPGA family from Intel® features lowerpower due to increased use of hardIPblocks MitySOM5CSx Single or Dual Arm® Cortex® and User Programmable FPGA SOM Critical Link’s MitySOM5CSx combines the Cyclone® V SoC from Intel®, memory subsystems, and onboard power supplies into a small formfactor SOM. Cyclone®VSoC devices are also offered in a lowpower variant, as indicated by the L power option in the device part number These devices have 30% static power reduction for devices with 25K LE and 40K LE, and % static power reduction for devices with 85K LE and 110K LE. Hello, I am using the CycloneV 5CSXFC6C6U23I7 SoC According to the specifications cyclone V, SX models should allow for a core frequency of up to.

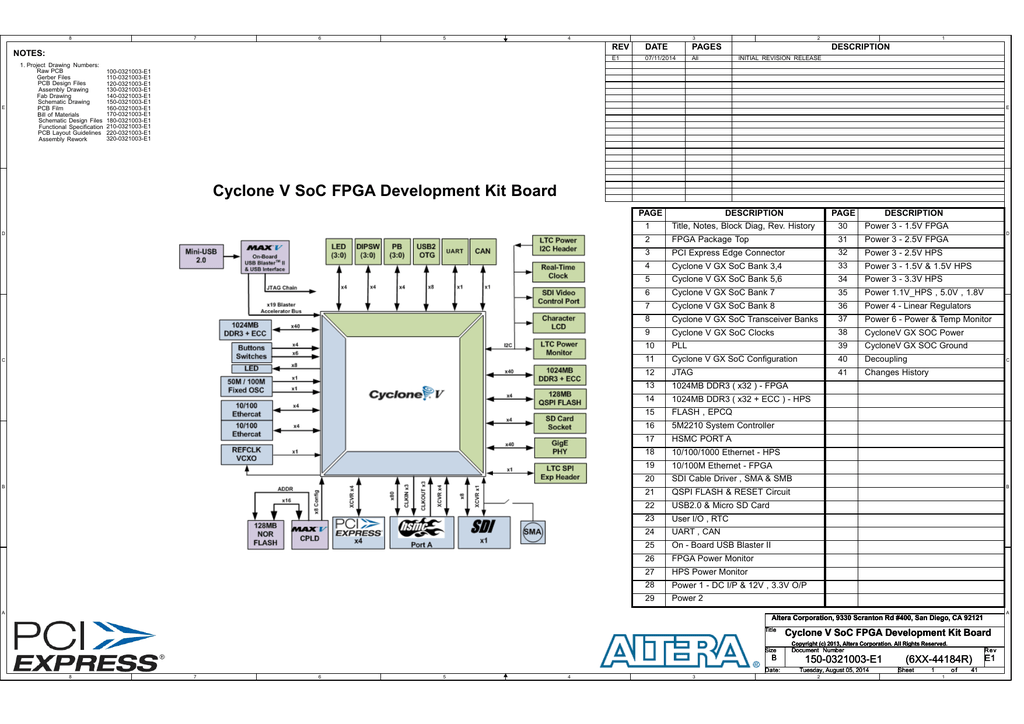

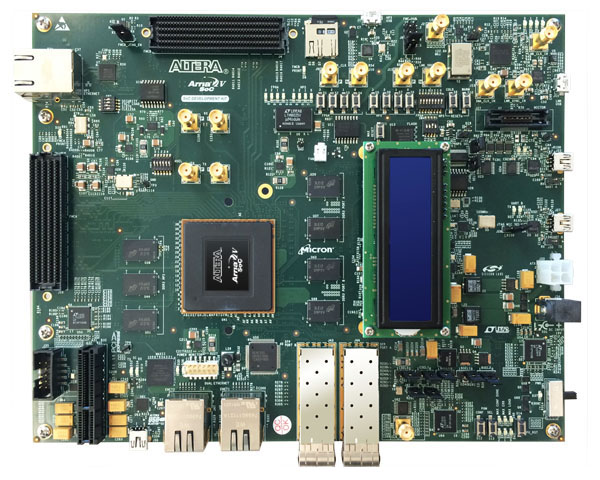

• Cyclone V SoC 5CSXFC6D6F31 Device • Dualcore ARM Cortex (HPS) • 110K Programmable Logic Elements • 5,140 Kbits embedded memory • 6 Fractional PLLs • 2 Hard Memory Controllers • 3125G Transceivers Configuration and Debug • Quad Serial Configuration device – EPCQ256 on FPGA • OnBoard USB Blaster II (micro USB type B. Cyclone V SoC and Arria V SoC For Cyclone V SoC and Arria V SoC, the handoff information created by Quartus compilation comes in several formats C source code, XML and binary files Bspeditor takes this information and turns it into source code which is used to build UBoot. Introduction This design example demonstrates how to use Cyclone V SoC with Triple Speed Ethernet (TSE) example design release packages It leverage on Altera Ethernet soft IP implemented in FPGA and used Modular ScatterGather Direct Memory Access (mSGDMA) IP for data transfer within the system The purpose of this design example is to serve as a starting point for TSE system designs with SoC.

The Cyclone® V SoC FPGA includes a sophisticated highperformance multicore ARM* Cortex* processor This processor can be used for a wide range of functions from very simple baremetal applications running on one of the available cores to highbandwidth, lowlatency, realtime operations. Cyclone V Devices" chapter in the Cyclone V Device Handbook These pins are not used in the JTAG configuration scheme Tie the MSEL pins to GND if your device is using the JTAG configuration scheme AS_DATA0/ ASDO/ DATA0 Bidirectional In a passive serial (PS) or fast passive parallel (FPP) configuration scheme, DATA0 is a dedicated input data pin. CYCLONE V SoC BANK 6 (HPS) 5 5 4 4 3 3 2 2 1 1 D D C C B B A A VCCIO = 33V VCCIO = 33V VCCIO = 33V VCCIO = 33V 10 5 3 3 GPIO HDMI TX User Interface (FPGA) 5 5 1 3 3 6 3 3 SD Card Interface.

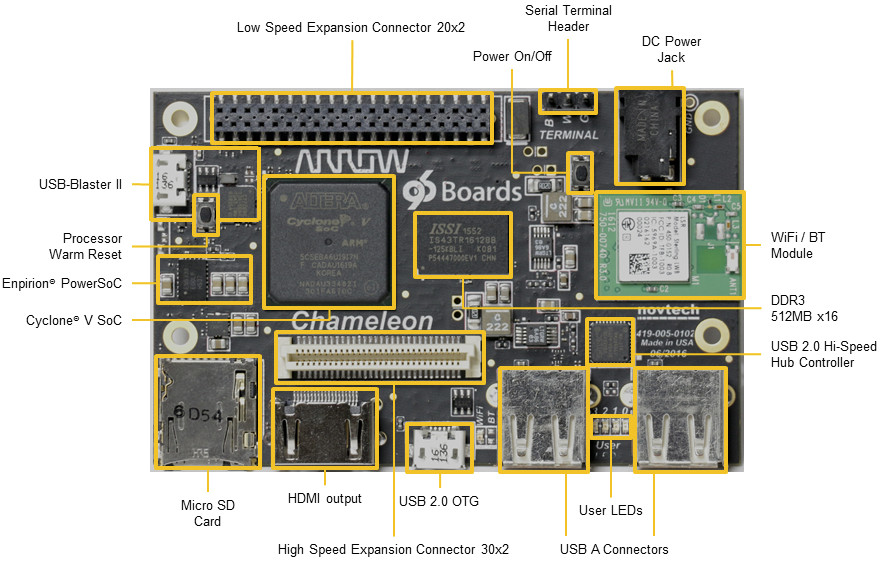

The Chameleon96™ board, based on Intel® Cyclone V SoC FPGA, is a member of 96Boards community and complies with Consumer Edition board specifications The Chameleon96™ meets all 96Boards mandatory specifications (excluding MIPI SDI Interface) and most optional specifications The Chameleon96™ features Dual ARM Cortex processors and a set of peripherals allow direct interfacing and. You'll get up to 40 percent lower total power compared with the previous generation, efficient logic integration capabilities, integrated transceiver variants, and SoC FPGA variants with an ARM*based hard processor system (HPS) Purchase the Cyclone® V GX Starter Kit for only $179 Compare 0/4. Intel®'s Cyclone® V SoCs provide the industry's lowestsystem cost and power The SoCs’ highperformance levels are ideal for differentiating highvolume applications such as industrial motor control drives, protocol bridging, video converter and capture cards, and handheld devices.

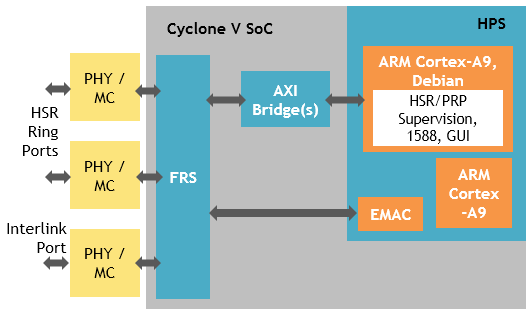

Altera Cyclone V SoC has 2 Ethernet Media Access Controller (EMAC) peripherals embedded along with the core in the Hard Processor System (HPS) Each EMAC can be used to transmit and receive data at 10/100/1000 Mbps over Ethernet connections in compliance with the IEEE 8023 specification. Downloads for the Terasic* DE10Nano kit featuring an Intel* Cyclone V FPGA SoC (). Cyclone® V SoC FPGAs offers a powerful dualcore ARM* Cortex* MPCore* processor surrounded by a rich set of peripherals and a hardened memory controller The FPGA fabric, with up to 110K LEs (logic elements), is connected to the hard processor system (HPS) through a highspeed >100 Gbps interconnect backbone Intel® Enpirion® Power Solutions.

Cyclone® V FPGAs provide the industry’s lowest system cost, lowest power FPGA solution as well as small formfactor package options (as small as 11x11 mm2) These advantages, along with its performance and logic utilization, result in devices optimized for differentiating your highvolume applications. Arria V SoC Altera Arria V SoC Board;. Terasic Arria10 SoC Board HAN Pilot Platform;.

Cyclone® V SoC FPGAs provide the industry's lowest system cost and power The SoC FPGA highperformance levels are ideal for differentiating highvolume applications, such as industrial motor control drives, protocol bridging, video converter and capture cards, and handheld devices. Hello, I am using the CycloneV 5CSXFC6C6U23I7 SoC According to the specifications cyclone V, SX models should allow for a core frequency of up to. Understanding the Cyclone V The target in the DE10Nano is a FPGA Cyclone V 5CSEBA6U23I7, this is a different type of FPGA because besides the programmable logic you also have an ARM Dual Core embedded into the SoC hardware in the same chipset This target FPGA has a lot of things, it's not interesting to list all here, but in the DE10 we.

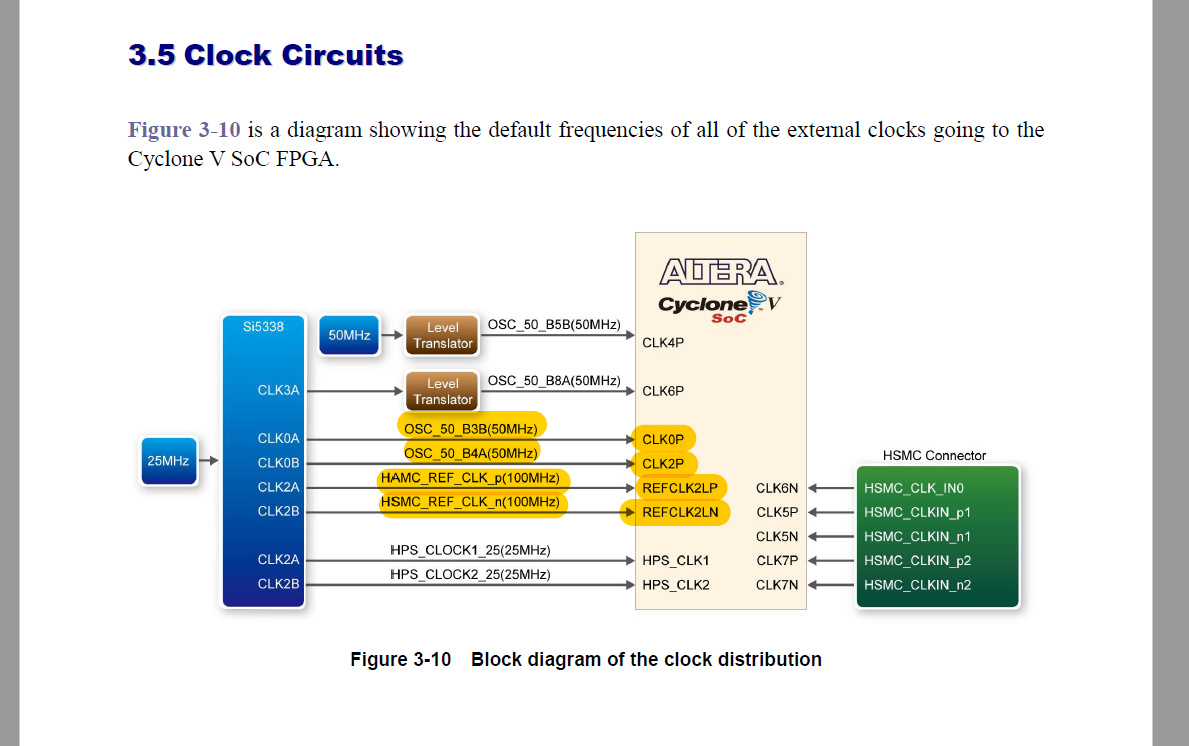

How to write a C/C application and run on the Altera Cyclone V SoC Dev Kit using ARM DS5 AE Follow Intel FPGA to see how we’re programmed for success and. Intel® Cyclone® 10 GX FPGA Intel® Cyclone® 10 GX FPGAs provide 125G transceiverbased functions, 14 Gbps LVDS, and up to 72 bit wide DDR3 SDRAM interface at up to 1,866 Mbps Intel® Cyclone® 10 GX FPGAs are optimized for highbandwidth performance applications, such as machine vision, video connectivity, and smart vision cameras. Cyclone V GX SoC Clocks Cyclone V GX SoC Configuration DDR3 Part 1 of 2 Ethernet PHY & RJ45 QDRII SRAM QSFP Interface Power 3 5V, 15V, 18V, 33V HSMC Port A & Port B Power 6 Power & Temp Monitor DDR3 Part 2 of 2 Power 4 10V_GXB, 15V_FPGA 34 Decoupling Power 8 Cyclone V GX SoC GND Preliminary Schematic DO NOT COPY Title Size.

The Chameleon96™ board, based on Intel® Cyclone V SoC FPGA, is a member of 96Boards community and complies with Consumer Edition board specifications The Chameleon96™ meets all 96Boards mandatory specifications (excluding MIPI SDI Interface) and most optional specifications The Chameleon96™ features Dual ARM Cortex processors and a set of peripherals allow direct interfacing and. 4,450 Kbits embedded memory. SoC HPS Address Map and Register Descriptions For more information on register level details, refer to the SoC HPS Address Map and Register Descriptions web page AN734 1509 HPS Method 3 CPU1 in WFI/WFE or Standby Loop 3 Cyclone V SoC Power Optimization Altera Corporation Send Feedback.

Arrow SoCKit User Manual November 19 Edition;. System on Module with Altera Cyclone V SoC Borax SOM is a system on module card integrating Altera® Cyclone® V SoC and necessary memory, power and external interfaces on a very small size card Cyclone V SoC is a new SoC tightly coupling with Dualcore ARM Cortex and FPGA fabric, enabling easy development of complex systems with advanced application processing and flexible hardware using. You need to have the development board with Intel (Altera) Cyclone V SoC I used SoCKit board I've been doing all the things described in this article in Debian Jessie You can use other Linux system or Windows with corresponding changes And you need DS5 IDE And, unfortunately, free edition doesn't allow you to compile a baremetal code.

System on Module with Altera Cyclone V SoC Borax SOM is a system on module card integrating Altera® Cyclone® V SoC and necessary memory, power and external interfaces on a very small size card Cyclone V SoC is a new SoC tightly coupling with Dualcore ARM Cortex and FPGA fabric, enabling easy development of complex systems with advanced application processing and flexible hardware using. Category Design Example Name Cyclone V SoC Hello World Description This example describes how to build a trivial hello world program using the linaro compiler in the SoC EDS tool chain. Cyclone V SoC Features Resources Product Line Cyclone V SE SoCs1 Cyclone V SX SoCs 1Cyclone V ST SoCs 5CSE 5CSE 5CSEA5 5CSEA6 5CSXC2 5CSXC4 5CSXC5 5CSXC6 5CSTD5 5CSTD6 LEs (K) 25 40 85 110 25 40 85 110 85 110 ALMs 9,434 15,094 32,075 41,509 9,434 15,094 32,075 41,509 32,075 41,509.

MCV offers the full flexibility of the Altera Cyclone V SoC FPGA family It integrates an ARMbased hard processor system (HPS) consisting of processor, peripherals, and memory interfaces with the FPGA fabric using a highbandwidth interconnect backbone The Altera SoCs combine the performance and power savings of hard intellectual property (IP) with the flexibility of. Download design examples and reference designs for Intel® FPGAs and development kits. Arrow SoCKit Evaluation Board;.

Cyclone® V SoC FPGAs provide the industry's lowest system cost and power The SoC FPGA highperformance levels are ideal for differentiating highvolume applications, such as industrial motor control drives, protocol bridging, video converter and capture cards, and handheld devices. The Intel® Cyclone® V SoC FPGAs Support page contains information to help you get started with Cyclone V SoC FPGA designs, including videos, documentation, and training courses. The Altera Cyclone V SoC ARM Cortex Demo Application Hardware and software set up Although the RTOS demo presented on this page has been preconfigured to run on the Altera Cyclone V SoC Development Kit it can be adapted easily to run on any Cyclone V SoC evaluation board that provides access to one UART and one LED.

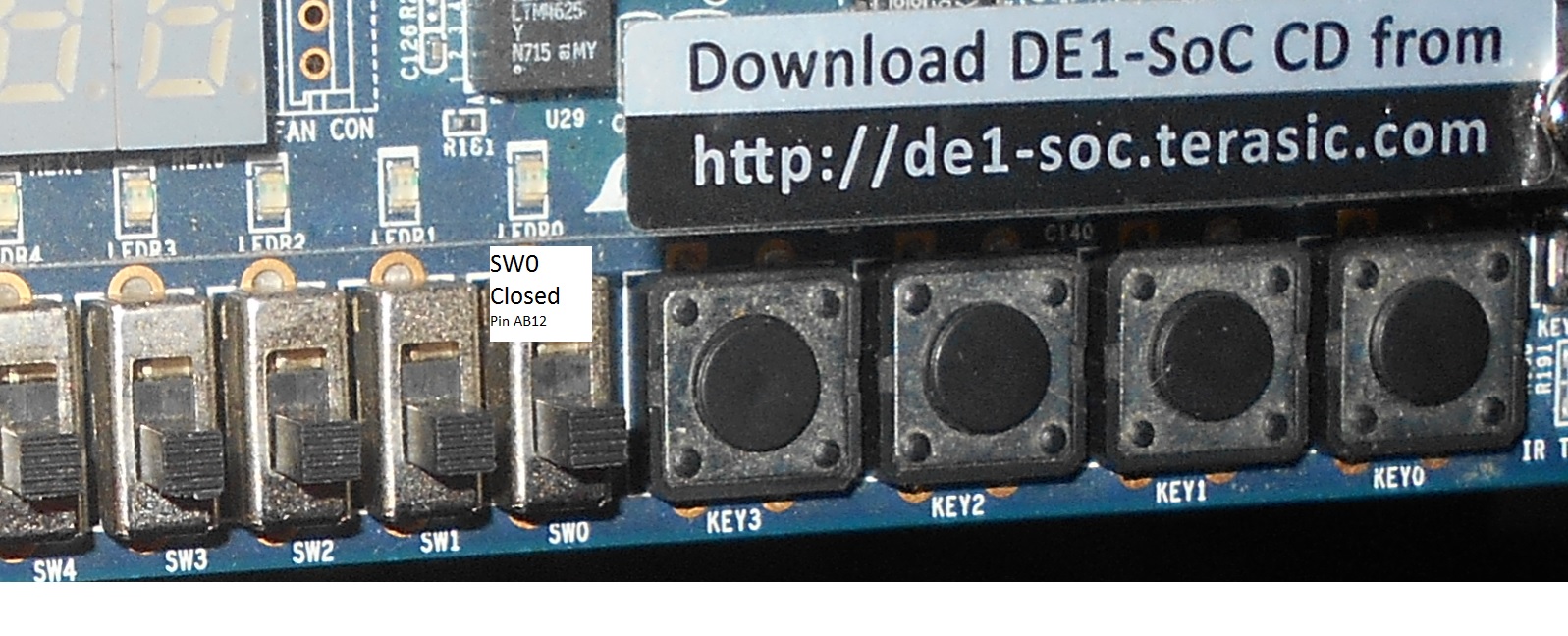

Hello, I am using the CycloneV 5CSXFC6C6U23I7 SoC According to the specifications cyclone V, SX models should allow for a core frequency of up to. Examples using the FPSoC chip Cyclone V SoC All these examples were tested on DE1SoC board However most of them are easily ported to other boards including Cyclone V SoC chips because they do not interact with the hardware in the board. The SoCKit Development Kit presents a robust hardware design platform built around the Altera Cyclone V SystemonChip (SoC) FPGA, which combines the latest Cortex embedded cores with industryleading programmable logic for ultimate design flexibility Users can now leverage the power of tremendous reconfigurability paired with a high.

How to configure and generate a basic SoC HPS (Hard Processor System) system using the Qsys system generation tool within the Quartus II software targeting t. The DE1SoC board has many features that allow users to implement a wide range of designed circuits, from simple circuits to various multimedia projects The following hardware is provided on the board FPGA Device Cyclone V SoC 5CSEMA5F31C6 Device;. Category Design Example Name Cyclone V SoC Hello World Description This example describes how to build a trivial hello world program using the linaro compiler in the SoC EDS tool chain.

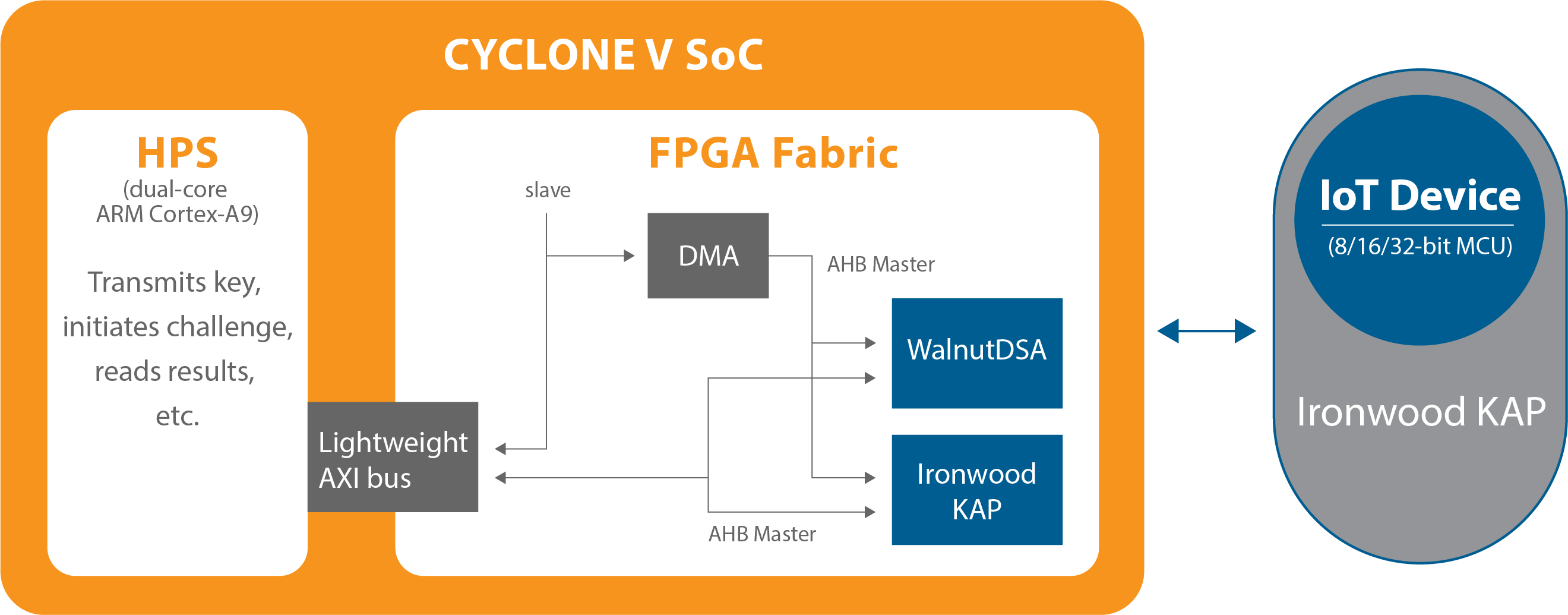

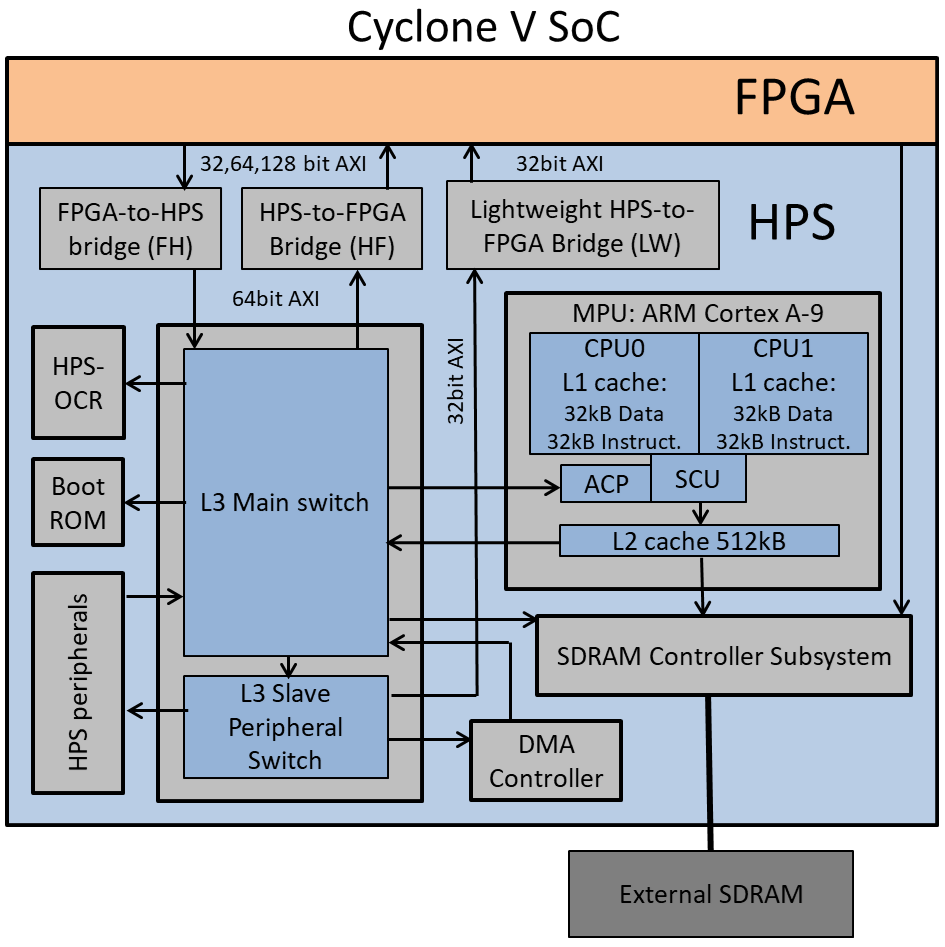

The CycloneV chip on the DE10, like other SoCFPGA designs, has a high speed data path directly from the ARM to the FPGA, and again in the reverse direction as shown in Fig 2These will form the topic of this article Today, I’d like to focus on the ARM side of this connection–the side where the FPGA is controlled by a CPUWe’ll ignore, and postpone for a later day, all of the details. The Altera Cyclone V SoC ARM Cortex Demo Application Hardware and software set up Although the RTOS demo presented on this page has been preconfigured to run on the Altera Cyclone V SoC Development Kit it can be adapted easily to run on any Cyclone V SoC evaluation board that provides access to one UART and one LED. For Cyclone V SoC and Arria V SoC, the handoff information created by Quartus compilation comes in several formats C source code, XML and binary files Bspeditor takes this information and turns it into source code which is used to build UBoot For older versions of SoC EDS, the user could set various UBoot parameters in bspeditor.

Cyclone V ST SoC with integrated Armbased HPS and 6144 Gbps transceivers Cyclone V E This section provides the available options, maximum resource counts, and package plan for the Cyclone V E devices The information in this section is correct at the time of publication For the latest. WiFi a/b/g/n Bluetooth 41 module interface. Intel Cyclone ® V 28nm FPGAs provide the industry's lowest system cost and power, along with performance levels that make the device family ideal for differentiating your highvolume applications You'll get up to 40 percent lower total power compared with the previous generation, efficient logic integration capabilities, integrated transceiver variants, and SoC FPGA variants with an ARMbased hard processor system (HPS).

About 34 month ago I am working with Cyclone V Soc boards (formerly revA, now revC ES board) FPGA portion usage I have managed to reach and test the DDR3 memory region clearly within FPGA portion by a Nios II soft core, and a videotest works in 1080p Nios II can reach and test/validate the memory in soft mode. Introduction This design example demonstrates how to use Cyclone V SoC with Triple Speed Ethernet (TSE) example design release packages It leverage on Altera Ethernet soft IP implemented in FPGA and used Modular ScatterGather Direct Memory Access (mSGDMA) IP for data transfer within the system. The SoCKit Development Kit presents a robust hardware design platform built around the Altera Cyclone V SystemonChip (SoC) FPGA, which combines the latest Cortex embedded cores with industryleading programmable logic for ultimate design flexibility Users can now leverage the power of tremendous reconfigurability paired with a high.

De1 Soc Altera Fpga Development Board Cyclone V Soc Aia Professional Agent

Cyclone V Fpga Family Intel Digikey

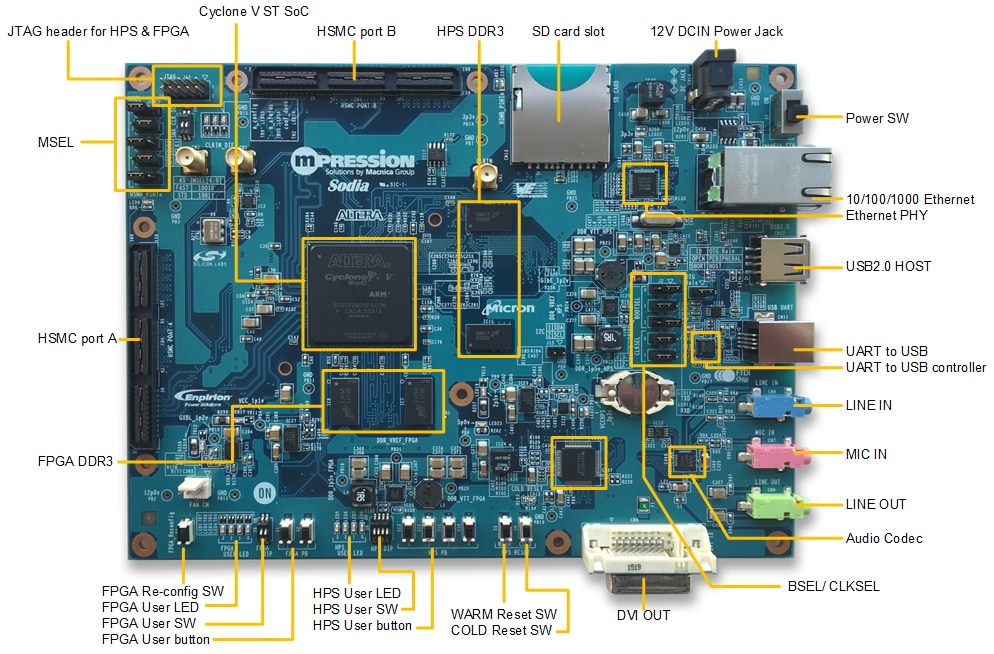

Cyclone V Soc Helio Board Macnica Cytech

Cyclone V Soc のギャラリー

Mercury Sa2 Cyclone V Soc Module

Board Test System Chapter 5 Board Test System Altera Cyclone V Soc User Manual Page 19 44

Mister Ported To Altera De1 Soc Fpga Modernhackers Com

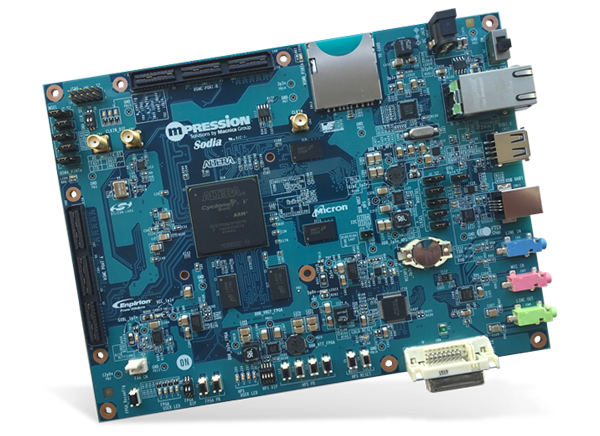

Sodia Cyclone V Soc Evaluation Board Mpression Mouser

Cyclone V Soc Fpgas With Tsn Intel Digikey

Cyclone V Soc Module Novsomcvlite

Cyclone V Soc Multi Port Ethernet Aggregator Board Netleap

Arrow Chameleon96 Board To Feature Intel Altera Cyclone V Se Fpga Arm Soc In 96boards Form Factor

Terasic All Fpga Boards Cyclone V Sockit The Development Kit For New Soc Device

Sodia Cyclone V Soc Evaluation Board Mpression Mouser

Terasic Cyclone V Soc Starter Kit De10 Nano

Intel Iot Cpu Fpga Security Veridify

Cyclone V Soc Qseven Development Platform Iwave Systems Technologies Pvt Ltd Pdf Catalogs Technical Documentation Brochure

Cyclone V Soc Development Kit And Soc Embedded Design Suite

Iotedge Soc Fpga Azure Iot Edge Module For Controlling An Intel Cyclone V Soc Fpga Microsoft Tech Community

Cyclone5 Structure

Why Drive On Chip Will Make Ethernet The Manufacturing Network Automation World

Terasic All Fpga Boards Cyclone V De0 Nano Soc Kit Atlas Soc Kit

Cyclone V Soc Fpgas Intel Soc Fpga

Critical Link Cyclone V Soc Module For Image Processing

Cyclone V Soc Development Kit And Soc Embedded Design Suite

De10 Nano Development Kit Terasic Technologies Mouser

Mitsubishi Electric S Next Generation Melsec Iq R Series C Controller Powered By Altera Socs To Enable Smarter Factories

Aries Embedded Mcv System On Module Documentation Rocketboards Org

.jpg)

Intel Cyclone Soc Fpga Price And Development Board Introduction Fpga Technology Fpgakey

380 63 De1 Soc Arm Fpga Development Board Altera Youjing Cyclone V Soc Second Zedboard From Best Taobao Agent Taobao International International Ecommerce Newbecca Com

351 35 Youjing Altera De1 Soc Cyclone V Soc Fpga Development Board Sends Matching Material Of Original Edition From Best Taobao Agent Taobao International International Ecommerce Newbecca Com

Getting Started With The Cyclone V Soc Development Kit Youtube

Risc V And Cyclone V Fpgas Supported By Ude

Enclustra Fpga Solutions Mercury Sa2 Intel Cyclone V System On Chip Soc Module System On Module Som 5cstfd6d5

Cyclone V Soc Fpgas Intel Soc Fpga

Terasic Cyclone V Soc Starter Kit De10 Nano

Dk Dev 5csxc6n Reference Design Field Programmable Gate Array Arrow Com

Terasic Soc Platform Cyclone Cyclone V Soc Development Kit And Soc Embedded Design Suite

Socrates Ii Reference Design Is Your New Shortcut To Fast Processing

Mpression Borax Som Module And Development Kit By Macnica Documentation Rocketboards Org

Module Altera Cyclone V Soc Avec De Nombreuses E S

Atlas Soc Development Platform Documentation Rocketboards Org

Dev Board Runs Linux On Altera Arm Fpga Soc

De1 Soc De1 Soc Fpga Development Board Cyclone V Soc 5csema5f31c6 Abs Sensor Aliexpress

Dk Dev 5csxc6n Reference Design Field Programmable Gate Array Arrow Com

Cyclone V Soc Development Kit And Soc Embedded Design Suite

Building A Bare Metal Application On Intel Cyclone V For Absolute Beginners Habr

Altera Cyclone V Soc Board Documentation Rocketboards Org

Fpga Master Based On Chip Communications Architecture For Cyclone V Soc Running Linux Semantic Scholar

Cyclone V Soc开发板原理图 Manualzz

Altera Cyclone V Soc Development Platform Documentation Rocketboards Org

Mpression Helio Soc Evaluation Kit By Macnica Documentation Rocketboards Org

Cyclone V Soc Helio Board Macnica Cytech

Cyclone V Socs Intel Digikey

239 25 De10 Nano Altera Fpga Development Board Cyclone V Soc Industrial Dual Core Arm From Best Taobao Agent Taobao International International Ecommerce Newbecca Com

De10 Nano Development Kit Is The Perfect Development Platform For Developers To Experience The Design Flexibility Blog Space

Dk Dev 5csxc6n Reference Design Field Programmable Gate Array Arrow Com

Cyclone V Soc Fpga Development Kits Enable Software Design Arrow Com

Terasic Cyclone V Soc Development Kit With Hsmc Connector De10 Standard

Terasic All Fpga Boards Cyclone V De1 Soc Board

Cytech Announces Evaluation Board For Altera S Cyclone V Soc Device Macnica Cytech Pte Ltd

Mitysom 5csx From Critical Link Llc Military Aerospace Electronics

News Events Flexibilis

Run Openwrt On Cyclone V Soc Documentation Rocketboards Org

Hybrid Fpga Soc Chips Hands On Embedded Programming With C 17

Altera Cyclone V Soc Qseven Module Offered By Iwave Systems

Sodia Cyclone V Soc Evaluation Board Mpression Mouser

New Mitysom A10s And Mitysom 5csx Features Intel Altera Arria 10 Soc And Intel Altera Cyclone V Soc Processor Respectively

Soc Fpga Family Altera Intel Mouser

Little Mego Soc Cyclone V Soc Development Board Dual Core Arm Fpga Linux Class Zynq

Dk Dev 5csxc6n Reference Design Field Programmable Gate Array Arrow Com

Arm Fpga Development Board Altera Friends Crystal Dual Nucleus Cyclone V Soc De10 Standard

Cyclone V Soc Helio Board Macnica Cytech

Open Sbc Runs Linux On Altera Arm Fpga Soc

Cyclone V Soc Qseven Module Ates Group

Macnica Mpression Helio View Cyclone V Soc Platform Circuit Note Analog Devices

Cyclone V Soc Module Us02a Microsom

Terasic Soc Platform Arria Arria V Soc Development Kit And Soc Embedded Design Suite

Terasic All Fpga Boards Cyclone V Terasic Soc System On Module Evaluation Kit

Cyclone V Soc Helio Board Macnica Cytech

Cyclone V Github Topics Github

Video Playback Demo On Cyclone V Soc Youtube

Playing With The Cyclone V Soc System De0 Nano Soc Kit Atlas Soc Digibirds Side

Soc Cyclone V Soc Development Board Dual Core Arm Fpga Linux A351

Launching Bare Metal Applications On Cyclone V Soc Sudo Null It News

Denx Mcv Systems On Module Feature Altera Cyclone V Sx Fpga Arm Soc

239 25 De10 Nano Arm Fpga Development Board Altera Friendly Crystal Double Core Plate Cyclone V Soc From Best Taobao Agent Taobao International International Ecommerce Newbecca Com

Tiny Module Runs Linux On Altera Arm Fpga Soc

Enclustra Ties 258 User I Os To Altera Cyclone V Soc

Fpga Master Based On Chip Communications Architecture For Cyclone V Soc Running Linux Semantic Scholar

Machine Vision Application On Iwave S Cyclone V Soc Development Platform Iwave Systems

249 Terasic Sockit Development Kit Features Altera Cyclone V Sx Dual Core Fpga Soc

Kopica Davor Munda S P Soc Cyclonev Bydp7

Altera Ships Its First Cyclone V Soc Devices Embedded Com

Correct Pin Assignment For Clock Input Of Cyclone V Soc Rocketboards Forum

Programmable Sdr Kit On Altera Cyclone V Soc And Adi Ad9361 Hsmc Youtube

1 Pcs X Chameleon96 Kit Cyclone V Soc Fpga Dual Core Arm Cortex Development Board Integrated Circuits Aliexpress

Tiny Module Runs Linux On Altera Arm Fpga Soc

Cyclone V Soc Qseven Development Kit Iw Rainbow G17d Iwave Systems Technologies Pvt Ltd

Github Uvidte Fpsoc Cyclonevsoc Time Measurements Processor Fpga Transfer Rate Measurements In Cyclonev Soc

Veek Mt2s Fpga Development Board Altera Youjing Cyclone V Soc De10 Standard